# Intel® Serial Flash Memory (S33)

16-, 32-, and 64-Mbit

### **Datasheet**

# **Product Features**

- Architecture

- SPI-compatible serial interface

- Eight 8-Kbyte parameter blocks; configurable as one 64-Kbyte main memory

- 64-Kbyte main memory sectors

- 16 Mbit (31 sectors)32 Mbit (63 sectors)

- 64 Mbit (127 sectors)

- Voltage and Power

- Vcc = 2.7 V to 3.6 V

- Standby current: 15 μA (Typ)

- Read current: 3 mA (Typ) at 33.3 MHz; 6 mA (Typ) at 68 MHz

- Performance

- 68-MHz fast read; 33.3 MHz standard read

- 256-byte program buffer

- Software

- Driver and file manager

- - One-Time Programmable Space

- 64 unique factory device identifier bits

- 64 user-programmable OTP bits

- Additional 3920 user-programmable OTP

- Quality and Reliability

- Operating temperature: -40 °C to +85 °C

- 100K minimum erase cycles per sector (block)

- 0.13 μm ETOX™ VIII process

- Density and Packaging

- 16, -32, -64-Mbit densities in SOIC-16 package

- 16-Mbit density in SOIC-8 package

- Industry standard packaging and pinout

Order Number: 314822-001US

August 2006

www.DataSheet4U.com

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See http://www.intel.com/products/processor\_number for details.

The Intel® Serial Flash Memory (S33) device may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, Dialogic, FlashFile, i960, InstantIP, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead. Intel. Leap ahead. logo, Intel NetBurst, Intel NetMarge, Intel NetStructure, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, IPLink, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

August 2006

Order Number: 314822-001US

\*Other names and brands may be claimed as the property of others.

Copyright © 2006, Intel Corporation. All Rights Reserved.

# Contents

| 1.0    | Intro               | duction        |                                     | 7    |

|--------|---------------------|----------------|-------------------------------------|------|

|        | 1.1                 | Nomen          | clature                             | 7    |

|        | 1.2                 | Acrony         | ms                                  | 7    |

|        | 1.3                 | Conven         | tions                               | 8    |

| 2.0    | Func                | tional O       | verview                             |      |

|        | 2.1                 |                | y Maps                              |      |

| 2.0    | Da ala              |                | ormation                            |      |

| 3.0    |                     | _              |                                     |      |

|        | 3.1<br>3.2          |                | Package                             |      |

|        |                     |                | -                                   |      |

| 4.0    | Pino                |                | Signal Descriptions                 |      |

|        | 4.1                 |                | Pinout (16-Mbit)                    |      |

|        | 4.2                 |                | 6 Package Pinout                    |      |

| et4U.c | :0 <del>1</del> 113 | Signal         | Descriptions                        | . 14 |

| 5.0    | Maxi                | mum Ra         | tings and Operating Conditions      | 15   |

|        | 5.1                 | Absolut        | e Maximum Ratings                   | 15   |

|        | 5.2                 | Operati        | ng Conditions                       | 15   |

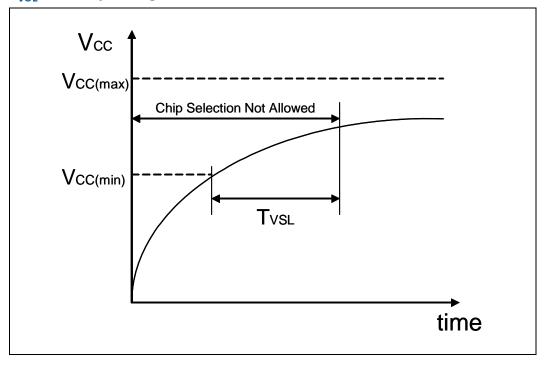

|        | 5.3                 | Powers         | Supply                              |      |

|        |                     | 5.3.1          | Power-Up/Down Characteristics       |      |

|        |                     | 5.3.2          | Power Supply Decoupling             | 16   |

| 6.0    | Elect               | rical Ch       | aracteristics                       | 17   |

|        | 6.1                 | DC Cur         | rent Specifications                 | 17   |

|        | 6.2                 | DC Volt        | age Specifications                  | 17   |

|        | 6.3                 | Capacit        | ance                                | 18   |

| 7.0    | AC C                | haracte        | ristics                             | 19   |

|        | 7.1                 |                | Conditions                          |      |

|        | 7.2                 |                | ing Characteristics                 |      |

|        |                     | 7.2.1          | Serial Input Characteristics        |      |

|        |                     | 7.2.2          | Write Protect Setup and Hold Timing | 21   |

|        |                     | 7.2.3          | Output Timing                       |      |

|        |                     | 7.2.4          | Hold Timing                         |      |

|        |                     | 7.2.5          | Other Timings                       | 23   |

| 8.0    | Devi                | ce Opera       | ations                              | 24   |

|        | 8.1                 | SPI Bus        | operations                          | . 24 |

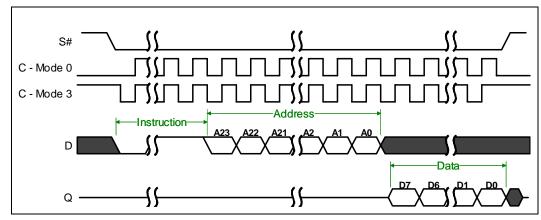

|        |                     | 8.1.1          | SPI Modes                           |      |

|        |                     | 8.1.2          | The Hold State                      |      |

|        | 8.2                 |                | mmand Set                           |      |

|        |                     | 8.2.1          | Write SPI SR Command (01h)          |      |

|        |                     | 8.2.2<br>8.2.3 | Page Program Command (02h)          |      |

|        |                     | 8.2.4          | Read Data Bytes Command (03h)       |      |

|        |                     | 8.2.4          | Read SPI SR Command (04h)           |      |

|        |                     | 8.2.6          | Write Enable Command (06h)          |      |

|        |                     | 8.2.7          | Fast Read Data Bytes Command (0Bh)  |      |

|        |                     | 8.2.8          | Clear SR Fail Flags Command (30h)   |      |

|        |                     | 8.2.9          | Parameter Block Erase Command (40h) |      |

|        |                     |                | OTP Program Command (42h)           |      |

|        |                     |                | Read OTP Data Bytes Command (4Bh)   |      |

|        |                     | 8.2.12         | Read ID Command (9Fh)               | .30  |

|          |         | 8.2.13 Release from DPD Command (ABh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30  | כ |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|

|          | 8.3     | Status Register Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |   |

|          |         | 8.3.1 Main Memory Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |   |

|          | 8.4     | SPI Instruction Cycle Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |   |

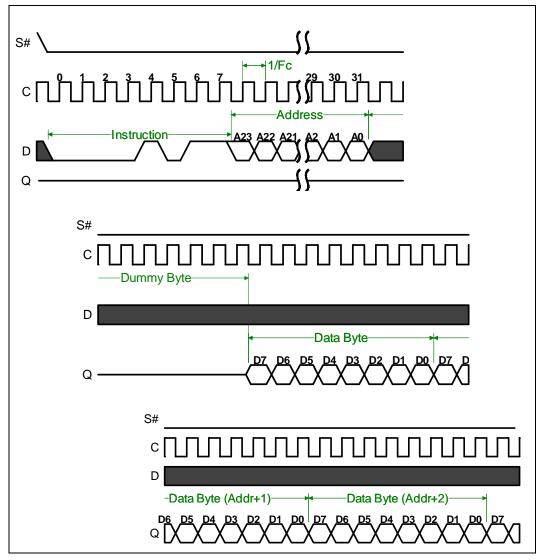

|          |         | 8.4.1 Fast Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33  | 3 |

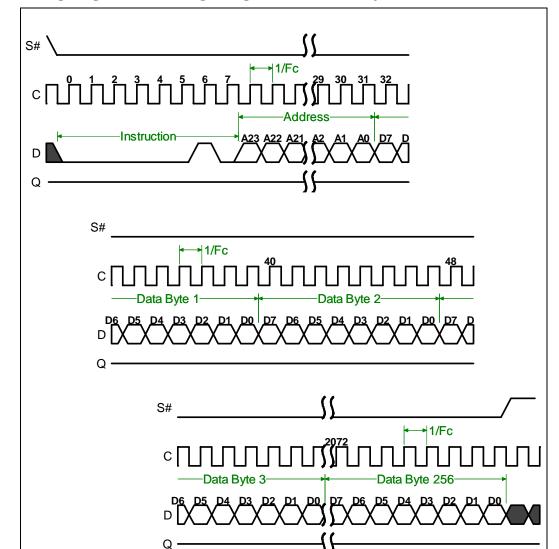

|          |         | 8.4.2 Page Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |   |

|          |         | 8.4.3 Write Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36  | 5 |

| 9.0      | Secur   | rity Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37  | 7 |

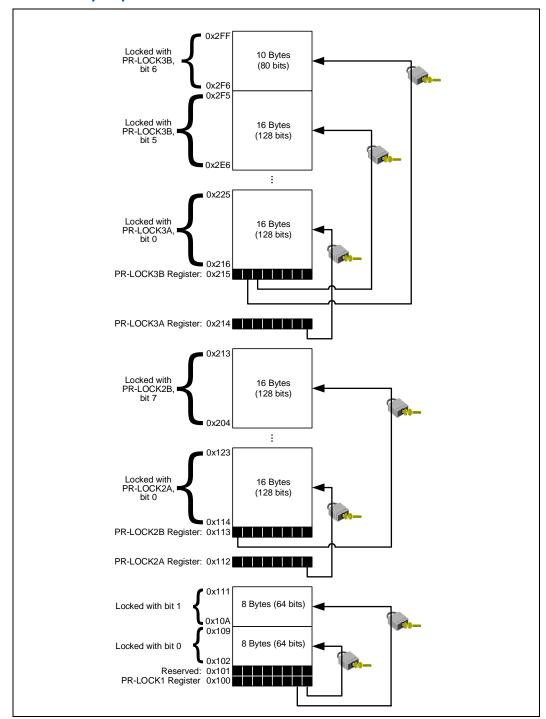

|          | 9.1     | OTP Memory Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |   |

|          |         | 9.1.1 Programming OTP Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |   |

|          |         | 9.1.2 Reading OTP Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |   |

|          |         | 9.1.3 Lock Protection Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37  | 7 |

| 10.0     | Intel®  | l <sup>®</sup> Serial Flash Memory (S33) ID Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39  | 9 |

| 814 L    | agiit a | A Write State Machine (WSM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40  | ٦ |

|          |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |   |

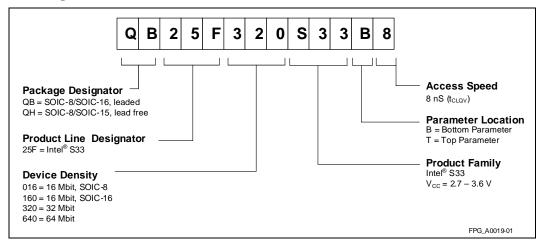

| Appe     | ndix B  | B Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42  | 2 |

|          |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |   |

| Figu     | rac     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |   |

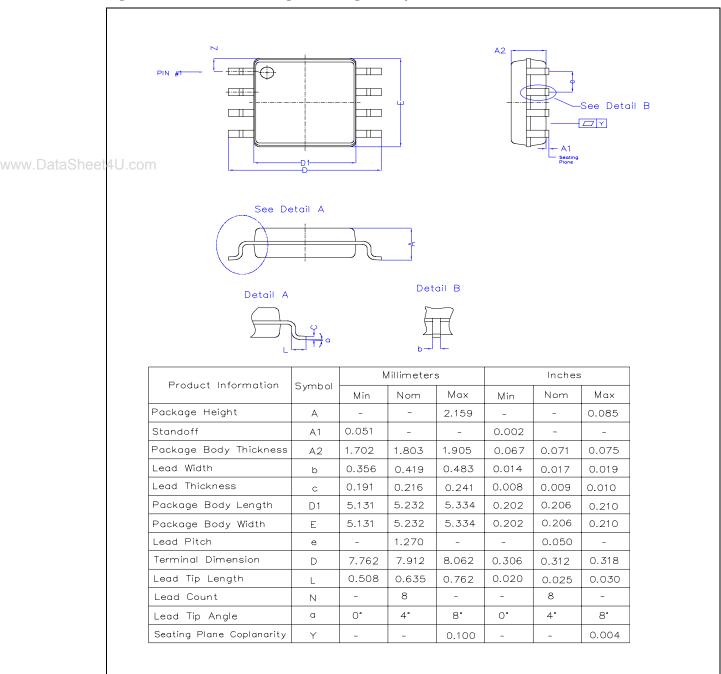

| 1        |         | IC-8 Package Drawing and Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 1 | 1 |

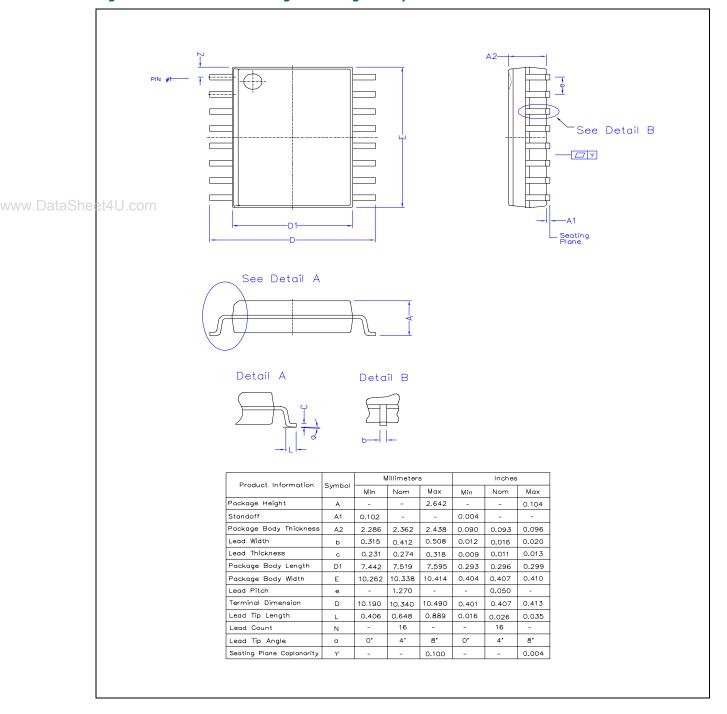

| 2        |         | IC-16 Package Drawing and Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |   |

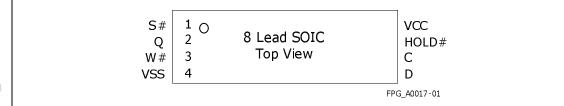

| 3        |         | IC-8 Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |   |

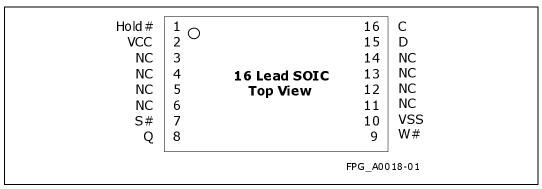

| 4        |         | IC-16 Package Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |   |

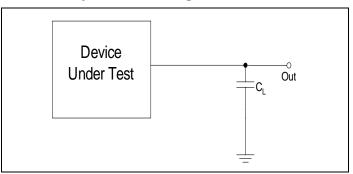

| 5        |         | nsient Equivalent Testing Load Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |   |

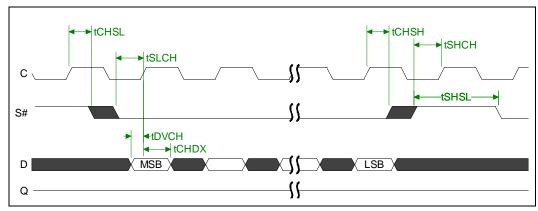

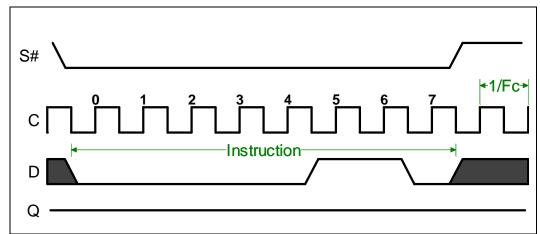

| 6        | Seria   | ial Input Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20  | ) |

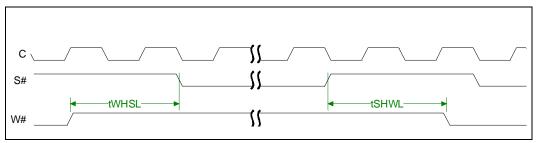

| 7        |         | te Protect Setup and Hold Timing during WRSR when SRWD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |   |

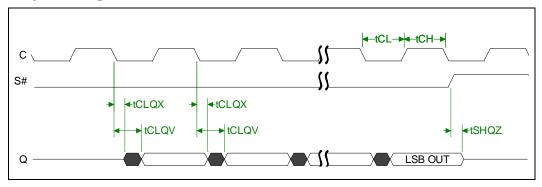

| 8        |         | tput Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |   |

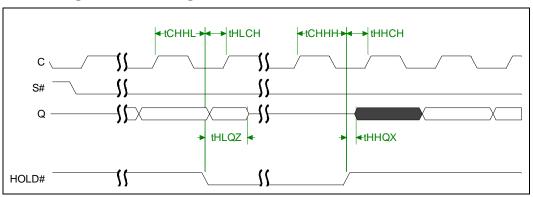

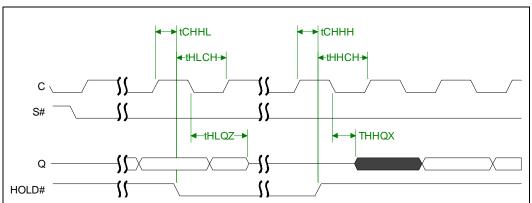

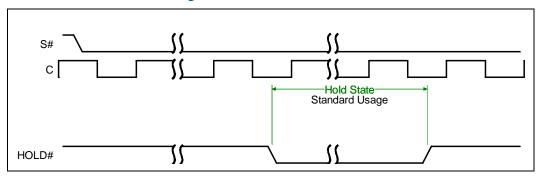

| 9        |         | d Timing - Standard Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |   |

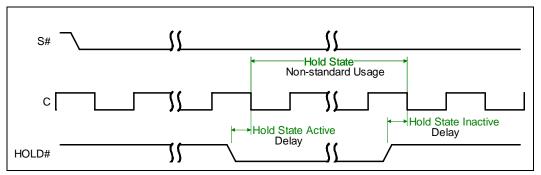

| 10       |         | d Timing - Non-standard Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |   |

| 11<br>12 |         | <sub>iL</sub> Power-up Timing<br>oported SPI Bus Operation Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |   |

| 13       |         | d State — Standard Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |   |

| 14       |         | d State – Non-standard Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |   |

| 15       |         | ning Diagram for SPI Fast Read Command Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |   |